Chipchain genomförde tape-out av 16nm FinFET MPW CyberShuttle

Från att ha erhållit TSMC:s 16nm PDK-teknikdokumentation, tog det ChipChains FoU-team cirka 4 månader att slutföra designverifieringen genom kontinuerlig optimering. Den 6 november skickades GDS-data officiellt till TSMC för tillverkning med 16nm MPW Shuttle.

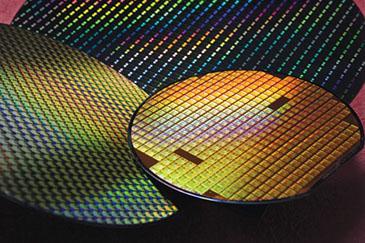

MPW-tjänsten innebär att flera integrerade kretsdesignkopior (copy) med samma teknik placeras på samma wafer för bearbetning. Varje design kan få tiotals chipsprover som används för experiment och valideringstester under produktutvecklingsfasen. MPW-tillverkningskostnaden delas av alla projekt som deltar i MPW baserat på chipets yta, vilket avsevärt minskar kostnaden under FoU-fasen för integrerade kretsar. Denna tjänst från TSMC gav ChipChains FoU-ingenjörer relativt flexibla förutsättningar, vilket effektivt främjade djärva innovationer i design och utveckling.