Chipchain a réalisé le tape-out de la navette MPW 16nm de TSMC

Après avoir obtenu les documents techniques du procédé 16 nm de TSMC, l’équipe de recherche et développement de Chipchain a passé environ 4 mois à optimiser et à valider le design. Le 6 novembre, ils ont finalement soumis les données GDS à TSMC pour une fabrication de puces sur un Shuttle MPW en 16 nm.

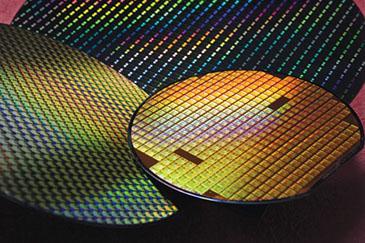

Le service MPW consiste à placer plusieurs conceptions de circuits intégrés utilisant le même procédé sur une même tranche de silicium pour la fabrication. Chaque conception peut recevoir des dizaines d’échantillons de puces, utilisés pour des tests expérimentaux et de validation pendant la phase de développement. Les coûts de fabrication MPW sont partagés entre tous les projets participants en fonction de la surface occupée par chaque puce, réduisant ainsi considérablement les coûts de développement des circuits intégrés. Ce service de TSMC a offert aux ingénieurs de Chipchain des conditions relativement flexibles pour des pratiques audacieuses, favorisant ainsi l’innovation dans la conception et le développement.