Chipchain führt Tape-Out des 16nm-FinFET-MPW-CyberShuttle durch

Von der Erlangung der TSMC-16-nm-PDK-Technologiedaten an arbeitete das F&E-Team von Chipchain etwa vier Monate lang an ständigen Optimierungen, bis es schließlich die Designvalidierung abschloss und am 6. November die GDS-Daten offiziell bei TSMC einreichte, um das Tape-Out mit dem 16-nm-MPW-Shuttle durchzuführen.

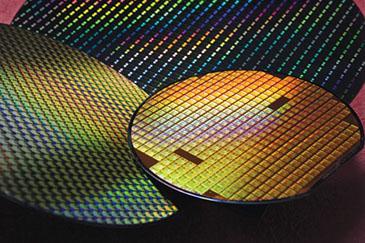

Der MPW-Dienst kopiert mehrere integrierte Schaltungsdesigns mit demselben Prozess auf einen einzigen Wafer, um eine Tape-Out-Bearbeitung durchzuführen. Jede Designvariante kann Dutzende von Chipmustern erhalten, die für Experimente und Validierungstests in der Produktentwicklungsphase verwendet werden. Die MPW-Tape-Out-Kosten werden von allen an der MPW teilnehmenden Projekten anteilig nach der belegten Chipfläche aufgeteilt, was die Kosten in der Entwicklungsphase der integrierten Schaltung erheblich senkt. Dieser Service von TSMC bot den Entwicklungsingenieuren von Chipchain relativ lockere Bedingungen für mutige Experimente und förderte wirksam die mutige Innovation im Entwicklungsdesign.